Welcome to the home page of the RTSIM

project. RTSIM stands for (Real-Time system SIMulator). It is

a collection of programming libraries written in C++ for

simulating real-time control systems.

RTSim has been developed at Retis Lab of the Scuola Superiore Sant'Anna as

an internal project. It has been used primarily for

experimenting with new scheduling algorithms and

solutions. For this reasons, it contains, already implemented,

most of the scheduling algorithms developed at Retis Lab.

We now decided to release this software as open source, to let

other researcher in the world to play with the simulator. The

dream is to have a common simulation platform for comparing

the performance of new scheduling algorithms.

RTSim is currently compatible with many systems, including

several distros of Linux, recent FreeBSD, Mac OS X and

Cygwin. In addition, the software has been tested with all

major releases of GCC, from 2.96 to 4.0.1. Under Windows, the

software can also be built using MinGW32.

Current version is 0.5, you can dowload from SourceForge at the

link below:

Get RTSim

Instructions for compiling and installing the software are in

the README file included in the distribution.

If you want to use the ctrlib features, you must also download

and install octave. We tried out this version of octave:

octave-2.0.16

However, many recent versions of octave have been successfully

tested with RTSim. Please read the README file for specific

per-version instructions, and possibly to set up for octave

usage (you may need to correct some errors in the octave headers

depending on which version of octave and GCC you have).

New in 0.5:

- GCC 4 support

- Dynamic libraries

- XML support using Xerces-C++

- C++ GUI based on Qt (versions 3 and 4)

- DLL support in Windows

New in 0.4:

- Full Autotools support (no more custom Makefiles)

- Compatibility with GCC 3.4

- Fully functional ctrlib

- No more "deprecated" warnings

- New ChangeLog and README

- Many changes under the hood

New in 0.3:

- changed Tick into a class

- rewritten the DAG algorithms

- rewritten the DRA algorithm

- moved JTracer to JDK 1.5 (no templates used though)

- renamed rtlib.h to rtlib.hpp

RTSIM consists of 4 components:

- metasim: it is a it is a generic library for simulation of

discrete event systems. This library is also released

separately, see the metasim

home page.

- rtlib: based on metasim, it is library for simulating

scheduling algorithms and real-time tasks.

- ctrlib (optional): it is a library for simulating

real-time control systems. It requires the octave

library.

- jtracer (optional): it is a java based tool for

visualisation of schedule traces produced by a rtlib

program.

Screenshots

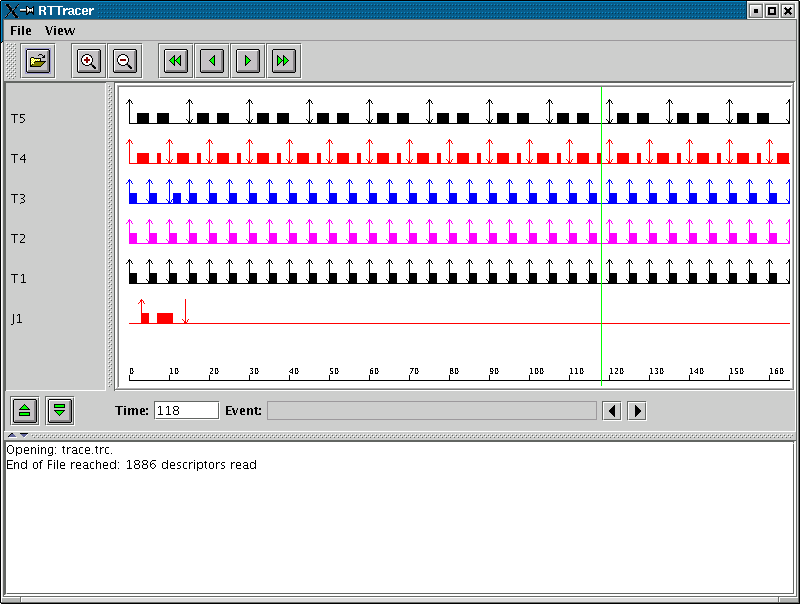

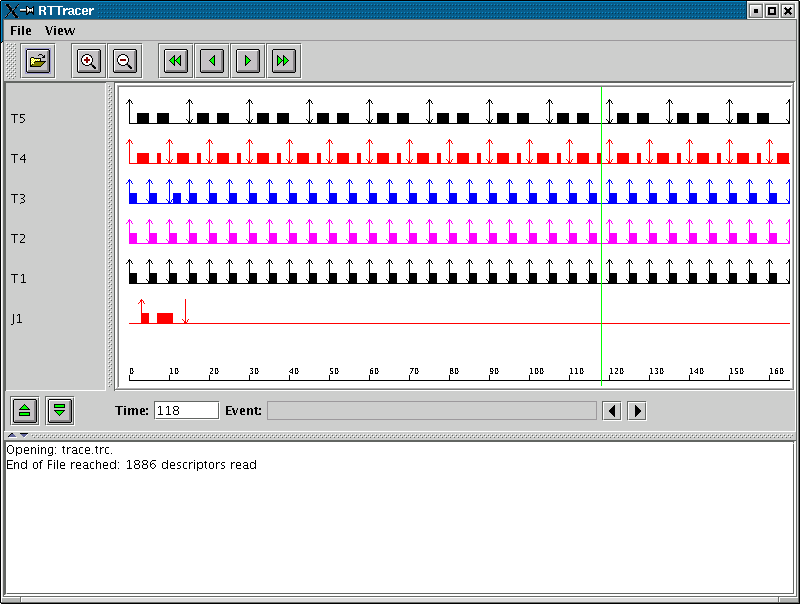

In the first screenshot you can see a jtracer window showing a

schedule of 5 periodic tasks (T1, ..., T5) plus one aperiodic

job (J1) on 3 processors, scheduled by EDF. This example is part

of the RTSIM distribution: you can find the source code in

rtsim/rtlib/examples/medf. On each line you can see the time

diagram of each task, and each task is shown in a different

color.

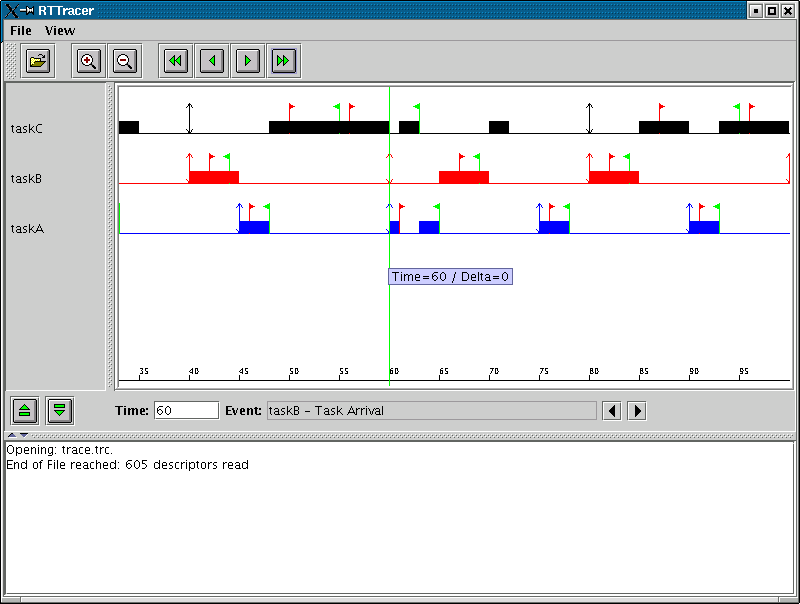

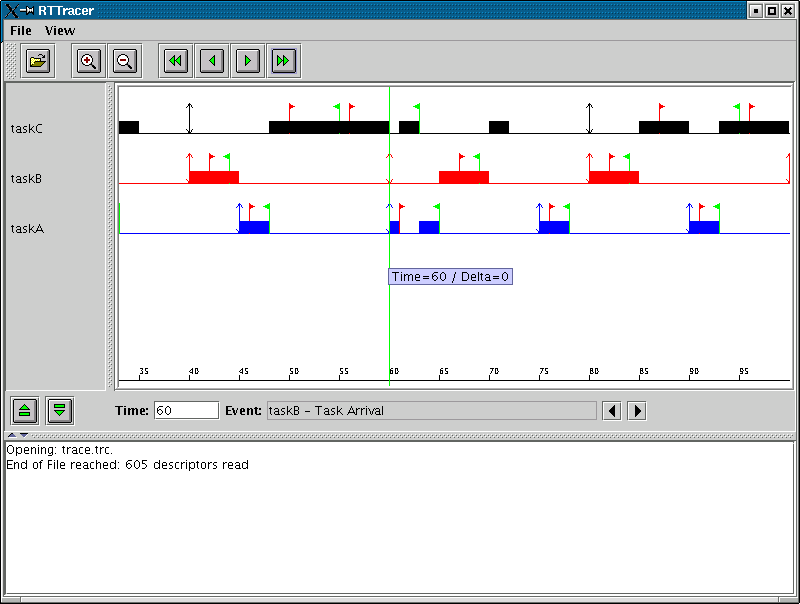

In this second screenshot, you can see three tasks scheduled on

one processor with fixed priority plus the priority inheritance

protocol. Each red flag represents a wait operation on a

semaphore, and each green flag represents a signal operation. In

the figure, task A is the highest priority task, task B is the

medium priority, and task C has the lowest priority.

Notice what happens at time 60: task A, which is the highest

priority task, tries to lock the resource, but it is blocked by

task C. Thanks to the priority inheritance mechanism, task C can

now execute with the priority of task A, thus executing before

tasks B.

As you can see, the priority inversion problem is avoided. This

example is part of the RTSIM distribution: you can find the

source code in rtsim/rtlib/examples/piresman.

If you want to ask any kind of question, report bugs or just

being informed of new releases, please use the SourceForge

website:

Bug report

Request for enhancements

Support forum

If you want to join the development of RTSIM, please contact the

project administrator at

this address.

Note that you will need a SourceForge account.

Cesare Bartolini

Giuseppe Lipari